Photovoltaic Carport Structure Photovoltaic Carport Structure,Solar Carport Mounting Structure System,Carport Mounting Structure System,Solar Energy System Metal Carports Hebei Shuobiao New Energy Technology Co., Ltd. , https://www.pvbracketsystem.com

A brief introduction to how to write code and generate download files

When remotely upgrading the FPGA code of a product, it's common to send an encrypted download file to the user, allowing them to perform the update locally. However, occasionally, due to oversight, the update may contain errors, leading to unexpected behavior or system failure after being downloaded. If the issue isn't urgent, it's best to communicate with the user and resend the corrected file. But for systems that require continuous operation, even a short delay can cause significant problems and downtime.

To avoid such issues, it's highly recommended to implement multiple configuration functions during remote FPGA upgrades. This allows the device to fall back to a stable version if the new update fails, ensuring uninterrupted operation.

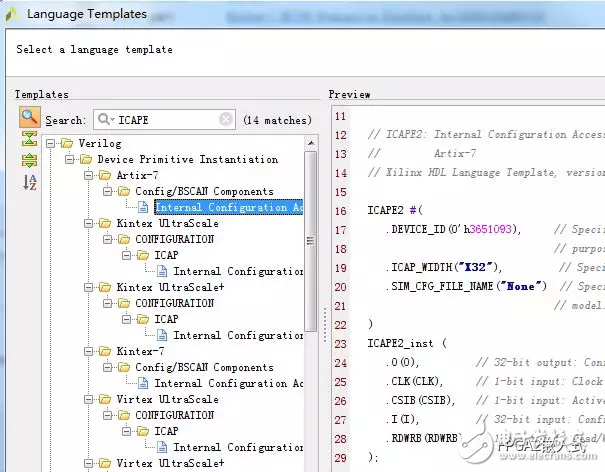

1. **ICAPE Core**

When using multiple configuration features, the ICAPE core must be integrated within the FPGA. It is responsible for executing the IPROG instructions, which are essential for switching between configurations. You can find the ICAPE core source in Vivado under "Language Templates" by searching for "ICAPE." The same applies to ISE tools.

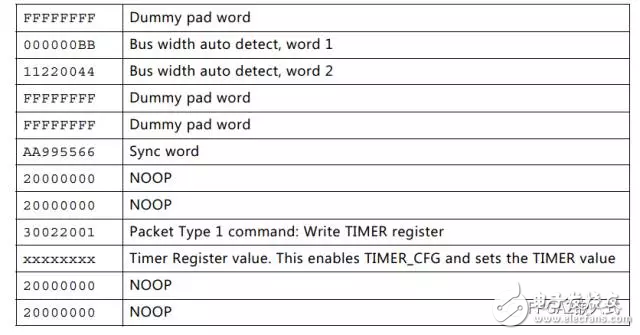

*IPROG configuration command*

2. **Multiple Configuration Code**

The multi-configuration code is stored alongside the original program in Flash memory. The old program is placed at address 0, while the update is stored afterward. Upon power-up, the FPGA reads from address 0 and uses the ICAPE core in the original program to decide whether to load the new configuration.

The update program does not need the IPROG code, as explained earlier. This setup ensures that if the new configuration fails, the system automatically reverts to the previous working version.

3. **Packaging Multiple Configuration Files**

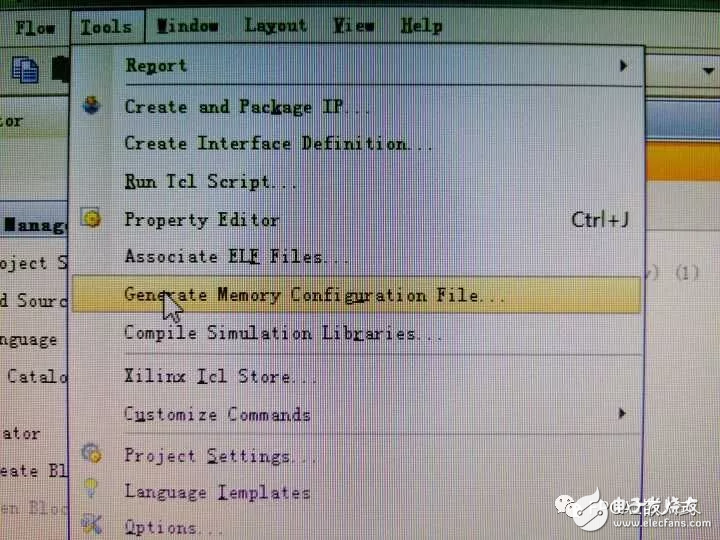

In Vivado, when generating an .xdc file, you must also include the Flash memory configuration. For example, set the Flash to SPI mode and define the read/write speed. Afterward, merge the two .bit files into one .mcs file.

To generate the .mcs file, go to the "Tools" menu and select "Generate Memory Configuration File." Choose the Flash device, set the read/write rate, and select the update file. Click OK to complete the process.

*Generating the .mcs file*

Once generated, the .mcs file can be sent to the user. If the update fails, the FPGA will automatically revert to the previous version, ensuring the device continues to operate normally.

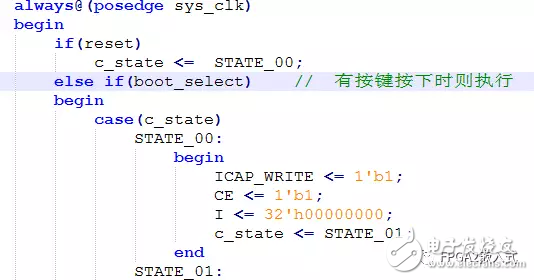

For added control, you can integrate external signals, like a button, into the ICAPE core logic. When the button is pressed, the FPGA can reload the new configuration, while otherwise, it continues running the current version.

*Adding control signals to the ICAPE core*

4. **Conclusion**

This section provides a brief overview of how to implement multiple configuration features for remote FPGA updates. Following these steps allows for more reliable and safe firmware upgrades, especially in mission-critical systems. By leveraging the ICAPE core and proper packaging of configuration files, users can enjoy a more robust and error-tolerant upgrade process.