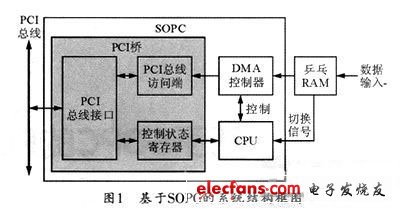

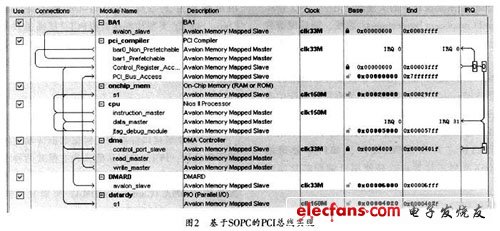

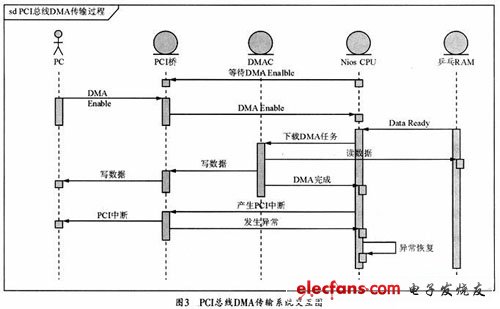

PCI (Peripheral CompONent Interconnect) bus, that is, the peripheral component interconnect bus, is currently the most widely used high-speed synchronous bus. Under a 32-bit bus width of 33Mz clock, its theoretical maximum transmission rate can reach 132Mbyte / s (64-bit bus It can reach 528Mbyte / s when the width is 66MHz), so it has become the preferred implementation method of the high transmission rate and low cost PC interface in the above reconnaissance receiving system. At present, there are two common methods for implementing the PCI bus interface: one is to use a special PCI bridge chip to implement the PCI interface, such as the PCI905X series chips of PLX Company; the other is to use a programmable chip to implement the PCI interface. This paper proposes a design scheme that uses a programmable system-on-chip (SySTem-On-Programmable-Chip, SOPC) to implement a PCI bus high-speed data transmission system for reconnaissance receivers, and uses direct memory access (DIRect Memory Access, DMA) transmission methods Data transfer rate. 1 PCI bus interface scheme design In the PCI bus interface standard, according to the location of the initiator of the data transmission, the PCI interface has two working modes: slave mode and master mode. According to different working methods, DMA transmission methods can be divided into continuous DMA (ConTInuous DMA) and distributed DMA (Scatter-Gather DMA). 1.1 Selection of PCI mode In the PCI bus standard, the mode in which the PC initiates data transmission and reads / writes the PCI interface card is called the slave mode. This mode only requires the PCI interface device to have the function of a PCI slave device, and the interface logic is relatively simple; the main mode is that the PCI interface card actively reads and writes PC memory, and the PCI interface logic is relatively complex. Frequently requesting the PC to initiate data transmission will occupy the resources of the PC. In order to reduce the burden on the PC and make it have more resources for subsequent digital signal processing, in the reconnaissance receiving system, the transmission mode of the PCI interface card selects the main transmission mode . 1.2 Selection of DMA transmission method DMA is a data transmission mechanism that improves the data transmission rate and the efficiency of microprocessor use. Continuous DMA is used to realize the transmission of continuous data blocks, that is, in a DMA transfer, the device side read / write physical address continuously changes (reads memory space) or does not change (read IO port), and the PC side physical storage address changes continuously. Distributed DMA is used to realize the transmission of discontinuous data blocks. The starting read / write address and length of each transmitted data block can be different. It uses a register list to store the read / write starting address and length of each data block. During the DMA transfer process, the address and length information are automatically loaded from the linked list. The DMA application of the distributed mode is flexible, and its disadvantage is that it needs to reconfigure the value of the DMA control register after transferring a data block, and the speed is slightly slower than the continuous mode. In the reconnaissance receiving system, the DMA transmission mode selects the continuous transmission mode. 1.3 PCI bus DMA transmission scheme design The overall block diagram of the PCI interface is shown in Figure 1. The data is input into the ping-pong RAM buffer. The ping-pong switching signal informs the CPU that the data is ready. The CPU judges whether the PC is ready through the control status register of the PCI bridge. If the PC is ready, configure and start the DMA controller. Read data in the ping pong RAM, write data to the PCI bus access end, the PCI bus interface unit applies for and obtains the PCI bus access right, and sends the data to the PCI bus. 2 SOPC implementation of PCI bus interface SOPC is a flexible and efficient system-on-chip solution proposed by Ahera. It integrates the processor, memory, I / O ports, and some general function modules on a PLD device to form a programmable system-on-chip. The use of SOPC to develop the PCI bus interface in the reconnaissance receiver has the advantages of short development cycle and good system stability. 2.1 System implementation The internal structure of SOPC of PCI bus interface is shown as in Fig. 2. Four types of functional modules are used to implement the PCI bus DMA transmission system, which are the pci_comiler component (pci_c ompiler) that implements PCI bridge logic, the DMA controller (dma) responsible for data transmission, and the NiosII processor (cpu) that controls the entire SOPC The data program memory (onchip_mem), and the interface module (BA1, DMARD, and datardy) for the logical communication between the SOPC and external users. The above components are connected together through the avalon bus to form the SOPC. The interaction process between the functional modules of the PCI bus DMA transmission system is shown in Figure 3, and the process is described as follows: (1) CPU waits for PC to enable DMA transfer, after PC enables DMA, execute (2); (2) The PC waits for the data ready signal of the ping pong RAM. After the data is ready, execute (3); (3) The CPU writes the DMA read / write address and transfer length parameters into the DMA controller, enables the DMA controller, and the DMA controller starts data transmission, that is, the read port reads from the RAM through the DMARD interface, and the write port writes the data Write to PCI bridge, PCI bridge sends data to PCI bus; (4) When the transfer ends, the DMA controller generates an interrupt (IRQ1) to send to the CPU; (5) The CPU judges whether the transfer is completed, then sends an interrupt to the PC through the PCI bridge, and executes (1) to start the next DMA transfer; (6) When an abnormality occurs on the PCI bus, the PCI bridge logic interrupts the CPU, and the CPU queries the abnormal state and automatically recovers from the abnormality. Traffic Facilities,Waterproof Traffic Facilities,Outdoor Traffic Facilities,Traffic Control Devices Yangzhou Heli Photoelectric Co., Ltd. , https://www.heli-eee.com